- 您现在的位置:买卖IC网 > Sheet目录1201 > CDB4245 (Cirrus Logic Inc)BOARD EVAL FOR CS4245 CODEC

�� �

�

�

�CS4245�

�4.� APPLICATIONS�

�4.1�

�4.2�

�Recommended� Power-Up� Sequence�

�1.� Hold� RESET� low� until� the� power� supply,� MCLK1,� MCLK2� (if� used),� LRCK1� and� LRCK2� are� stable.� In�

�this� state,� the� Control� Port� is� reset� to� its� default� settings.�

�2.� Bring� RESET� high.� The� device� will� remain� in� a� low� power� state� with� the� PDN� bit� set� by� default.� The� con-�

�trol� port� will� be� accessible.�

�3.� The� desired� register� settings� can� be� loaded� while� the� PDN� bit� remains� set.�

�4.� Clear� the� PDN� bit� to� initiate� the� power-up� sequence.�

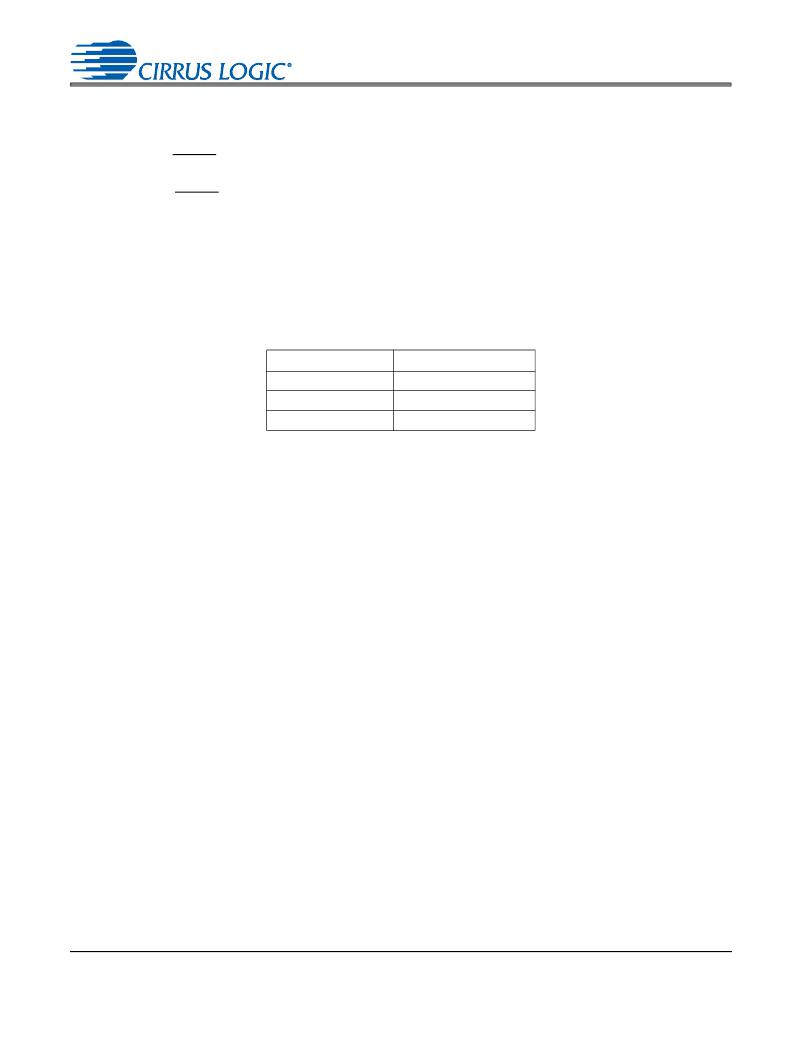

�System� Clocking�

�The� CS4245� will� operate� at� sampling� frequencies� from� 4� kHz� to� 200� kHz.� This� range� is� divided� into� three�

��Mode�

�Single-Speed�

�Double-Speed�

�Quad-Speed�

�Sampling� Frequency�

�4-50� kHz�

�50-100� kHz�

�100-200� kHz�

�Table� 1.� Speed� Modes�

�The� CS4245� has� two� serial� ports� which� may� be� operated� synchronously� or� asynchronously.� Serial� port� 1�

�consists� of� the� SCLK1� and� LRCK1� signals� and� clocks� the� serial� audio� output,� SDOUT.� Serial� port� 2� consists�

�of� the� SCLK2� and� LRCK2� signals� and� clocks� the� serial� audio� input,� SDIN.�

�Each� serial� port� may� be� independently� placed� into� Single,� Double,� or� Quad� Speed� mode.� The� serial� ports�

�may� also� be� independently� placed� into� Master� or� Slave� mode.�

�4.2.1�

�4.2.2�

�30�

�Synchronous� /� Asynchronous� Mode�

�By� default,� the� CS4245� operates� in� Synchronous� Mode� with� both� serial� ports� synchronous� to� MCLK1.� In�

�this� mode,� the� serial� ports� may� operate� at� different� synchronous� rates� as� set� by� the� ADC_FM� and�

�DAC_FM� bits,� and� MCLK2� does� not� need� to� be� provided� (the� MCLK2� pin� may� be� left� unconnected).�

�If� the� Asynch� bit� is� set� (see� “Asynchronous� Mode� (Bit� 0)”� on� page� 46� ),� the� CS4245� will� operate� in� asyn-�

�chronous� mode.� The� serial� ports� will� operate� asynchronously� with� Serial� Port� 1� clocked� from� MCLK1� and�

�Serial� Port� 2� clocked� from� MCLK2.� In� this� mode,� the� serial� ports� may� operate� at� different� asynchronous�

�rates.�

�Master� Clock�

�In� Asynchronous� Mode,� MCLK1/LRCK1� and� MCLK2/LRCK2� must� maintain� an� integer� ratio.� In� synchro-�

�nous� mode� MCLK1/LRCK1� and� MCLK1/LRCK2� must� maintain� an� integer� ratio.� Some� common� ratios� are�

�shown� in� Table� 2� .The� LRCK� frequency� is� equal� to� Fs,� the� frequency� at� which� audio� samples� for� each�

�channel� are� clocked� into� or� out� of� the� device.� The� ADC_FM� and� DAC_FM� bits� and� the� MCLK� Freq� bits�

�(See� “MCLK� Frequency� -� Address� 05h”� on� page� 45.� )� configure� the� device� to� generate� the� proper� clocks�

�DS656F3�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

CDB42L55

BOARD EVAL FOR CS42L55 CODEC

CDB44L11

EVALUATION BOARD FOR CS44L11

CDB48500-USB

KIT USB EVALUATION FOR CDB48500

CDB5378

EVALUATION BOARD FOR CS5378

CDB5460AU

EVALUATION BOARD FOR CS5460A

CDB5461AU

BOARD EVAL & SOFTWARE CS5461A

CDB5466U

BOARD EVAL & SOFTWARE CS5466 ADC

CDB5467U

BOARD EVAL FOR CS5467 ADC

相关代理商/技术参数

CDB42518

功能描述:音频 IC 开发工具 Eval Bd

RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V

CDB42528

功能描述:音频 IC 开发工具 Eval Bd

RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V

CDB4265

功能描述:音频 IC 开发工具 Eval Bd 192kHz CODEC w/PGA & Input Mux RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V

CDB4270

功能描述:音频 IC 开发工具 Eval Bd 105dB 192kHz CODEC

RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V

CDB4271

功能描述:音频 IC 开发工具 Eval Bd CS4271

RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V

CDB4272

功能描述:音频 IC 开发工具 Eval Bd CS4272

RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V

CDB4299

功能描述:音频 IC 开发工具 Eval Bd AC’97 CODEC w/SRC

RoHS:否 制造商:Texas Instruments 产品:Evaluation Kits 类型:Audio Amplifiers 工具用于评估:TAS5614L 工作电源电压:12 V to 38 V

CDB42L50

制造商:CIRRUS 制造商全称:Cirrus Logic 功能描述:Low Voltage, Stereo CODEC with headphone Amp